Kontekst historyczny: skąd wzięło się prawo Moore’a

Gordon Moore i lata 60. XX wieku

Prawo Moore’a narodziło się w czasach, gdy komputery wypełniały całe pokoje, a tranzystory wcale nie były jeszcze oczywistą technologią dominującą. Gordon Moore był współzałożycielem Fairchild Semiconductor, jednego z pierwszych dużych producentów układów scalonych, a później współzałożycielem Intela. Jego perspektywa nie wynikała z akademickich rozważań, ale z praktycznej obserwacji linii produkcyjnych, ograniczeń technologicznych i zamówień klientów.

W 1965 roku Moore opublikował artykuł w magazynie „Electronics” pod tytułem „Cramming more components onto integrated circuits”. Opisał w nim prostą, ale uderzającą obserwację: liczba elementów (tranzystorów, rezystorów, diod) na pojedynczym układzie scalonym rośnie wykładniczo, a konkretnie – podwaja się mniej więcej co rok. Wtedy mowa była o układach z dziesiątkami, potem setkami i tysiącami elementów, ale trend był jasny.

Moore nie próbował wróżyć z fusów. Porównał dostępne produkty, ich daty wprowadzenia na rynek i gęstość integracji, a następnie ekstrapolował linię trendu na kolejne lata. Co ważne, prognoza dotyczyła przede wszystkim liczby elementów na chipie, a nie „mocy obliczeniowej” czy „częstotliwości taktowania”, które później często błędnie utożsamiano z prawem Moore’a.

Dlaczego w ogóle ktoś w 1965 r. zdecydował się rysować tak śmiałą krzywą? Branża półprzewodnikowa była wtedy w fazie wczesnego wzrostu, a producenci i inwestorzy potrzebowali mapy drogowej (roadmapy), aby planować fabryki, sprzęt litograficzny, badania i rozwój. Skoro widać było, że kolejna generacja procesu pozwala „upchać” znacznie więcej elementów na tej samej powierzchni, sensownie było założyć, że przy odpowiednich nakładach da się utrzymać ten trend przez kilka kolejnych lat.

Ewolucja sformułowania „prawa”

Początkowa wersja przewidywania Moore’a mówiła o podwajaniu liczby elementów co rok. Już kilka lat później, patrząc na realia produkcji, Moore skorygował swoje twierdzenie do mniej agresywnej wersji: podwojenie liczby tranzystorów co około 18–24 miesiące. Ten sposób rozumienia utrwalił się na dekady jako „klasyczne” prawo Moore’a.

Z czasem „liczba tranzystorów” zaczęła być w mediach i marketingu zastępowana luźniejszymi pojęciami. Zaczęto mówić, że prawo Moore’a to wzrost „mocy obliczeniowej”, „wydajności procesorów” albo „postępu w IT”. To uproszczenie jest wygodne, ale technicznie nieprecyzyjne. Faktyczne brzmienie prawa dotyczyło gęstości integracji, a nie konkretnych wskaźników wydajności.

Prawo Moore’a stało się także klasycznym przykładem samo spełniającej się prognozy. Skoro cała branża – od producentów maszyn litograficznych, przez dostawców chemikaliów, po projektantów układów – przyjęła wykładniczy wzrost jako standard planowania, to harmonogramy inwestycji, budowa fabów i programy badawcze były ustawione właśnie po to, aby tę krzywą utrzymać. W praktyce nie tyle „prawo” opisywało naturę, ile wyznaczało tempo, które wszyscy usiłowali realizować.

Znaczenie przewidywalnych trendów dla rewolucji komputerowej

W latach 70., 80. i 90. przewidywalność, jaką dawało prawo Moore’a, była bezcenna. Inwestorzy widzieli, że co kilka lat pojawi się możliwość wytwarzania układów o znacznie większej złożoności, przy niższym koszcie pojedynczego tranzystora. To uzasadniało budowę coraz droższych fabryk i rozwijanie zaawansowanej litografii.

Z kolei producenci komputerów osobistych, serwerów czy urządzeń sieciowych mogli zakładać, że za 3–5 lat dostaną układy o wielokrotnie większej liczbie tranzystorów, przy zbliżonym lub niższym koszcie jednostkowym. Dzięki temu można było projektować oprogramowanie coraz bardziej wymagające, zakładając, że sprzęt „dogoni” potrzeby. To jedna z fundamentalnych przyczyn, dla których rewolucja komputerowa końca XX wieku nabrała takiego rozpędu.

Z perspektywy użytkownika końcowego prawo Moore’a przełożyło się na wrażenie permanentnego skoku technologicznego: komputer kupiony trzy lata wcześniej wydawał się toporny i wolny w porównaniu z nowym modelem. Jednocześnie cena sprzętu nie rosła proporcjonalnie do możliwości. Mechanizm: miniaturyzacja tranzystorów + spadek kosztu jednego tranzystora spowodował realne potanienie mocy obliczeniowej.

Prawo Moore’a nie jest więc „prawem fizyki” w stylu równań Maxwella, lecz empiryczną regułą, która stała się biznesową osią całej branży półprzewodników. Tempo jej realizacji – i to, czy wciąż jest możliwe – zależy zarówno od fizyki krzemu, jak i od zdolności finansowania coraz droższych technologii produkcji.

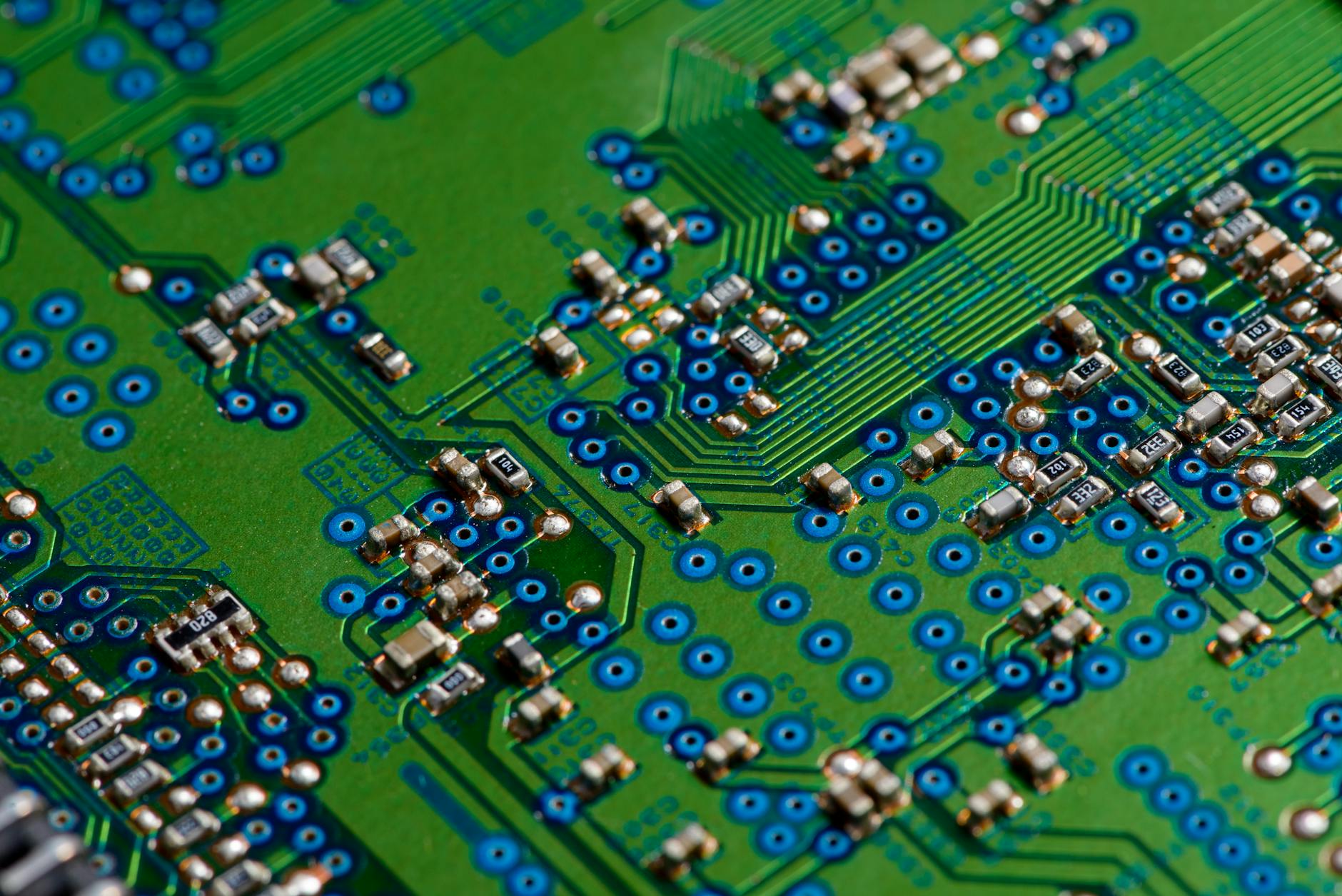

Podstawy techniczne: tranzystor, proces technologiczny, gęstość integracji

Tranzystor w układach scalonych: cyfrowy przełącznik

W kontekście procesorów, GPU i innych układów cyfrowych tranzystor jest przede wszystkim przełącznikiem. W uproszczeniu, napięcie na bramce tranzystora MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) decyduje o tym, czy między drenem a źródłem płynie prąd (stan logiczny „1”), czy nie (stan „0”). Na tej bazie buduje się bramki logiczne (AND, OR, NOT itd.), a z nich – rejestry, ALU, cache, kontrolery pamięci.

W nowoczesnych procesorach x86, ARM lub RISC-V używa się wyspecjalizowanych odmian tranzystorów MOSFET zoptymalizowanych pod kątem małych rozmiarów, szybkości przełączania i niskiego poboru mocy. Kluczowe typy to:

- Planarny MOSFET – dominował do około 28 nm; tranzystor „płaski”, kanał przewodzący prąd leży pod bramką w płaszczyźnie krzemu.

- FinFET – tranzystor z wystającym „płetwowym” kanałem (fin), który jest otoczony bramką z trzech stron. Poprawia to kontrolę nad kanałem i ogranicza prądy upływu.

- GAAFET (Gate-All-Around FET) – kanał ma postać nanodrutów lub nanosiatek, a bramka otacza go dookoła. To kolejny krok w kierunku lepszej kontroli elektrostatycznej i dalszej miniaturyzacji.

Każda nowa generacja tranzystora jest odpowiedzią na fizyczne problemy poprzedniej: rosnące prądy upływu, zbyt wysoką gęstość mocy, ograniczoną skalowalność. Z punktu widzenia prawa Moore’a istotne jest, że nowe struktury (FinFET, GAAFET) pozwalają dalej zwiększać gęstość upakowania bez katastrofalnego pogorszenia parametrów elektrycznych.

Węzeł technologiczny: 90 nm, 7 nm, 3 nm – co to dziś znaczy

Termin węzeł technologiczny (node) to nazwa danej generacji procesu litograficznego, w której produkowane są układy scalone. Historycznie liczba w nazwie – np. 180 nm, 90 nm, 45 nm – odnosiła się mniej więcej do długości bramki tranzystora albo minimalnej szerokości ścieżki metalowej, którą można było wyrysować na krzemie.

Przy węzłach rzędu 130 nm i powyżej te oznaczenia były stosunkowo spójne: długość bramki naprawdę miała wielkość zbliżoną do deklarowanej. Z biegiem czasu sytuacja się skomplikowała. Różne elementy tranzystora (długość kanału, wysokość płetwy, odległości między ścieżkami) skalowały się inaczej, do gry weszły zaawansowane techniki litografii wielokrotnej, a marketing producentów zaczął podkreślać „mniejszy numer” jako wyznacznik przewagi.

W rezultacie dzisiejsze nazwy węzłów – 7 nm, 5 nm, 3 nm – są w dużej mierze marketingowe. Realne długości bramek mogą mieć inne wartości, często większe. Różni producenci (TSMC, Samsung, Intel) stosują nieco inne konwencje nazewnicze. Dla analizy prawa Moore’a ważniejsze od samego „numerka” są:

- rzeczywista gęstość tranzystorów (liczba tranzystorów na mm²),

- dostępne napięcia zasilania i prądy upływu,

- koszt produkcji jednego mm² w danym węźle.

Przykładowo, węzeł „Intel 7” ma parametry zbliżone do „TSMC N7”, mimo różnych nazw i historii rozwoju. Z kolei „Intel 4” jest porównywalny z TSMC N5 pod względem gęstości tranzystorów. To pokazuje, że przy ocenie tempa rozwoju trzeba patrzeć głębiej niż na samą etykietę procesu.

Gęstość tranzystorów a rozmiar chipu i funkcjonalność

Gęstość tranzystorów (np. miliony tranzystorów na mm²) mówi, ile elementów logicznych można zmieścić na danej powierzchni krzemu. Im większa gęstość, tym na tej samej powierzchni można umieścić:

- więcej rdzeni CPU lub większe rdzenie o bardziej złożonej mikroarchitekturze,

- większe i szybsze pamięci cache,

- rozbudowane jednostki wektorowe, tensorowe, akceleratory AI, dekodery video,

- dodatkowe kontrolery peryferiów (PCIe, pamięci, interfejsy sieciowe).

Dla zobrazowania skali różnic warto zestawić orientacyjnie stare i nowe generacje układów. Przybliżone liczby pokazują trend, nie są jednak punktową miarą dokładności procesu.

| Układ | Rok | Proces technologiczny | Liczba tranzystorów (rzędu wielkości) |

|---|---|---|---|

| Procesor x86 klasy Pentium | lata 90. | 350–250 nm | dziesiątki milionów |

| Procesor desktopowy ok. 2010 | ok. 2010 | 45–32 nm | setki milionów do ponad miliarda |

| Nowoczesny CPU lub GPU wysokiej klasy | po 2020 | 7–3 nm | dziesiątki miliardów |

Z punktu widzenia prawa Moore’a najważniejsze jest, że liczba tranzystorów na chipie wciąż rośnie wykładniczo. Jednak sama ich liczba nie jest równoznaczna z liniowym wzrostem wydajności. Architektura ma równie duże znaczenie: zła mikroarchitektura może zmarnować miliardy tranzystorów, a dobra – wycisnąć maksimum z relatywnie prostego układu.

Dodatkowo, rozmiar fizyczny chipów też nie pozostaje stały. Duże GPU lub procesory serwerowe potrafią zajmować ponad 600–800 mm² krzemu, co jest bliskie praktycznej granicy ze względu na rozmiar wafla i prawdopodobieństwo defektów. To kolejny powód, dla którego w pewnym momencie pojawiły się pomysły omijania ograniczeń przez łączenie wielu matryc (chipletów) zamiast projektowania jednego monolitycznego giganta.

Złota era skalowania: Dennard, częstotliwość i spadek kosztów

Skalowanie Dennarda – „idealne” zmniejszanie tranzystorów

Prawo Moore’a mówi o rosnącej liczbie tranzystorów, ale nie tłumaczy jak ich zmniejszanie wpływa na moc i częstotliwość. Tu wchodzi koncepcja skalowania Dennarda z lat 70. Robert Dennard i jego współautorzy opisali, jak parametry tranzystora MOSFET zmieniają się przy jego zmniejszaniu, zakładając odpowiednie skalowanie napięć.

W idealnym modelu, jeśli wszystkie wymiary liniowe tranzystora zmniejsza się o współczynnik k (np. 0,7), to:

- pojemność bramki maleje,

- napięcie zasilania można proporcjonalnie obniżyć,

- czas przełączania się skraca, więc można zwiększyć częstotliwość,

- gęstość mocy (moc na jednostkę powierzchni) pozostaje mniej więcej stała.

To oznaczało, że mniejsze tranzystory są szybsze i bardziej energooszczędne, a przy tym nie powodują nadmiernego wzrostu temperatury chipu. Połączenie prawa Moore’a (więcej tranzystorów) i skalowania Dennarda (lepsze parametry każdego z nich) dało efekt lawinowy: co kilka lat procesory były jednocześnie mniejsze, szybsze i bardziej opłacalne.

Wzrost częstotliwości w latach 80., 90. i na początku XXI wieku

W praktyce skalowanie Dennarda przekładało się bezpośrednio na wyścig na częstotliwość. Procesory z lat 80. pracowały z zegarami rzędu kilku–kilkudziesięciu MHz. W latach 90. weszły w zakres setek MHz, a na przełomie stuleci przekroczyły 1 GHz. Kolejne generacje procesu technologicznego umożliwiały podnoszenie częstotliwości bez dramatycznego wzrostu poboru mocy.

Typowy schemat wyglądał tak:

- nowy proces – mniejsze tranzystory – niższe napięcie – krótsze czasy przełączania,

- wyższa częstotliwość taktowania przy zbliżonym TDP (Thermal Design Power),

Spadek kosztu na tranzystor i „darmowa” wydajność

Drugim filarem złotej ery było systematyczne obniżanie kosztu pojedynczego tranzystora. Gdy przechodziło się na mniejszy węzeł, na tym samym waflu krzemowym mieściło się więcej układów, a przy zbliżonym koszcie przetworzenia wafla koszt jednego tranzystora malał. To było paliwo ekonomiczne dla prawa Moore’a: nie tylko dało się upchnąć więcej tranzystorów, ale każdy z nich był tańszy.

Skalowanie Dennarda gwarantowało, że rosnąca liczba tranzystorów nie powodowała eksplozji poboru mocy. Deweloperzy dostawali więc „gratis” wyższe częstotliwości i większą wydajność jednowątkową, a producenci sprzętu mogli co generację podnosić parametry bez radykalnego zwiększania TDP i kosztu chłodzenia. Stąd wzięło się poczucie, że sprzęt „sam przyspiesza” – wystarczyło poczekać rok lub dwa, kupić nowy procesor i cieszyć się widocznym wzrostem FPS-ów lub krótszym czasem kompilacji.

Skutek uboczny był taki, że przez wiele lat optymalizacja oprogramowania była w cieniu. Wystarczało napisać poprawny kod, a kolejna generacja CPU „załatwiała” większość problemów z wydajnością. Ten model załamał się, gdy fizyka wystawiła rachunek za dalsze podbijanie częstotliwości.

Granice częstotliwości: napięcie, moc i ściana cieplna

Podbijanie częstotliwości nie jest darmowe. Moc dynamiczna tranzystora MOSFET można w dużym uproszczeniu zapisać jako:

P ≈ C × V² × f

gdzie C to pojemność obciążenia, V – napięcie zasilania, a f – częstotliwość zegara. W klasycznym skalowaniu Dennarda obniżano jednocześnie rozmiary tranzystora, pojemność i napięcie, więc przy wzroście częstotliwości moc na jednostkę powierzchni pozostawała mniej więcej stała.

Problem zaczął się wtedy, gdy napięcie przestało się skalować tak szybko. W okolicach 90–65 nm dalsze agresywne obniżanie Vdd (napięcia zasilania) powodowało zbyt duże spowolnienie tranzystorów i wzrost wrażliwości na szum, a prądy upływu (leakage) zaczęły rosnąć wykładniczo. Producenci w praktyce „zamrozili” napięcia w okolicach 1 V (zależnie od procesu), a to oznaczało, że jedyną prostą dźwignią zwiększania wydajności pozostała częstotliwość.

Po kilku generacjach procesów pojawiła się tak zwana ściana cieplna (thermal wall): dalsze zwiększanie częstotliwości powodowało nieproporcjonalny wzrost TDP, którego nie dało się już rozproszyć w typowej obudowie desktopa czy laptopa. W pewnym momencie podniesienie zegara o kilkanaście procent mogło oznaczać konieczność zwiększenia mocy o kilkadziesiąt procent. Bilans przestał się spinać – zarówno z perspektywy użytkownika (hałas, temperatura), jak i producenta (koszt chłodzenia, niezawodność, normy energetyczne).

Załamanie skalowania Dennarda i koniec wyścigu na GHz

Dlaczego skalowanie Dennarda przestało działać

Teoretyczne założenia Dennarda opierały się na idealizacjach: jednorodnym polu elektrycznym, nieskończonej precyzji litografii, zaniedbywalnych prądach upływu. W miarę schodzenia poniżej ~90 nm rzeczywiste zjawiska fizyczne zaczęły domagać się uwagi:

- Prądy upływu (leakage) przestały być pomijalne. Cienki tlenek bramki (gate oxide) powodował tunelowanie elektronów, więc tranzystor przewodził prąd nawet w stanie „wyłączonym”. To zwiększało pobór mocy spoczynkowej (static power), niezależny od częstotliwości.

- Zwiększony wpływ zjawisk kwantowych i szumów utrudniał dalsze obniżanie napięć zasilania i progowych. Zbyt niskie napięcie oznaczało, że tranzystor przestawał przełączać się w sposób przewidywalny przy rozsądnych marginesach bezpieczeństwa.

- Problemy z interkonektami (połączeniami metalowymi) stały się dominujące. Nawet jeśli sam tranzystor był szybki, sygnał musiał przebyć coraz dłuższą i węższą ścieżkę metalową z większą rezystancją i pojemnością pasożytniczą. Latencja przewodów zaczęła być porównywalna z czasem przełączania tranzystora.

- Nierównomierność skalowania – nie wszystkie wymiary dało się zmniejszać liniowo. Grubości warstw, wysokości finów, odległości między metalami wymuszały kompromisy, które burzyły elegancki model Dennarda.

Efekt końcowy był taki, że przy danym napięciu i określonych restrykcjach cieplnych kolejne generacje procesu technologicznego nie dawały już prostego, liniowego skoku częstotliwości. Wzrost zegara zaczął hamować, a w niektórych segmentach (laptopy, serwery) nawet się cofać na rzecz oszczędności energii.

Stagnacja częstotliwości: plateau wokół 3–4 GHz

Jeśli spojrzeć na wykres maksymalnych częstotliwości desktopowych CPU od końca lat 90., widać ostre wznoszenie do okolic 3–4 GHz na początku lat 2000, po czym… wielkie plateau. Współczesne procesory konsumenckie potrafią w turbo przekraczać 5 GHz, ale nie jest to fundamentalnie inny poziom niż Pentium 4, które biło rekordy w okolicach 3,8–4 GHz – różnica jest głównie w tym, jak długo i przy jakiej mocy taki zegar da się utrzymać.

Za tym plateau stoją twarde ograniczenia fizyczne:

- TDP i chłodzenie – przekroczenie 150–200 W w komputerze biurkowym wymaga rozbudowanych systemów chłodzenia; w laptopach typowe limity to 15–45 W, co niemal automatycznie kończy rozmowę o stałym taktowaniu 5 GHz na wszystkich rdzeniach.

- Straty w przewodach i tranzystorach – przy wysokich częstotliwościach rosną straty energii na przeładowywanie pojemności pasożytniczych, narasta też znaczenie sygnałów zakłócających i opóźnień propagacji.

- Marginesy bezpieczeństwa – aby utrzymać sensowny yield (odsetek działających układów z wafla), producenci muszą zostawiać margines na zmienność procesu (PVT – process, voltage, temperature). Wyśrubowanie częstotliwości „do granicy” drastycznie obniżyłoby opłacalność produkcji.

Dlatego zamiast ciągnąć dalej wykres w górę, producenci zaczęli szukać innych dróg zwiększania wydajności. Część z nich była oczywista (więcej rdzeni), inne wymagały znaczących zmian architektonicznych i programistycznych.

Przesunięcie akcentu: od GHz do rdzeni i równoległości

Jeśli nie da się już łatwo przyspieszyć pojedynczego tranzystora, można spróbować zwiększyć liczbę jednostek wykonawczych. To prosta idea, ale jej konsekwencje okazały się potężne dla całego ekosystemu.

Producenci CPU przestawili się na:

- wielordzeniowość – najpierw dwa, potem cztery, osiem i więcej rdzeni w jednym układzie,

- równoległość wewnątrz rdzenia (ILP, Instruction Level Parallelism) – szerokie jednostki superskalarne, przewidywanie skoków, wykonywanie spekulatywne,

- równoległość danych – rozbudowane jednostki SIMD (MMX, SSE, AVX, AVX-512) oraz akceleratory GPU.

Od strony sprzętu logika jest prosta: jeśli nie można już mnożyć częstotliwości, trzeba mnożyć ścieżki wykonawcze. Ale równoległość ma sens tylko wtedy, gdy oprogramowanie potrafi ją wykorzystać. To wymusiło upowszechnienie się wątków, bibliotek wielowątkowych, modeli dyskretnego równoległego programowania (OpenMP, TBB, CUDA, OpenCL) i zmianę sposobu myślenia o algorytmach.

Uwaga praktyczna: przejście z jednordzeniowego CPU 3 GHz na ośmiordzeniowy 3 GHz nie daje magicznego 8× przyspieszenia w typowych aplikacjach biurowych. Zgodnie z prawem Amdahla część kodu jest z natury sekwencyjna. Zwiększanie liczby rdzeni poprawia wydajność szczególnie w zadaniach masowo równoległych (rendering, symulacje, kompilacja wielomodułowa, przetwarzanie w chmurze), ale w codziennym surfowaniu po sieci kluczowa pozostaje wydajność jednowątkowa.

Wzrost znaczenia wydajności jednowątkowej i IPC

Skoro częstotliwość utknęła, a wielordzeniowość ma ograniczoną skalowalność z powodu natury oprogramowania, producenci CPU zaczęli inwestować coraz więcej w IPC (Instructions Per Cycle, liczba instrukcji na cykl). Cel: sprawić, by przy danym zegarze rdzeń wykonał jak najwięcej „pożytecznej pracy”.

Typowe techniki stosowane we współczesnych mikroarchitekturach to m.in.:

- Poszerzanie front-endu – dekodowanie większej liczby instrukcji na cykl, bardziej agresywne pobieranie i buforowanie instrukcji.

- Lepsze przewidywanie skoków – rozbudowane predyktory oparte na historii globalnej i lokalnej, redukujące liczbę błędnych przewidywań, które „marnują” cykle.

- Głębsze i szersze potoki wykonawcze – większa liczba portów wykonawczych, jednostek ALU/FPU, możliwość wykonywania wielu instrukcji równolegle (superskalarność).

- Większe i szybsze pamięci cache – ograniczające liczbę kosztownych dostępów do pamięci RAM.

- Spekulacja i wykonywanie poza kolejnością (out-of-order) – dynamiczne reorganizowanie kolejności wykonywania instrukcji tak, aby jak najlepiej wykorzystać dostępne jednostki wykonawcze.

Tego typu triki architektoniczne pozwoliły przez ostatnie lata zwiększać wydajność jednowątkową o kilka–kilkanaście procent na generację, mimo braku dramatycznych wzrostów częstotliwości. Z punktu widzenia użytkownika końcowego prawo Moore’a „przeobraziło się” – z prostego skoku MHz na bardziej złożone połączenie IPC, liczby rdzeni i specjalizowanych jednostek.

Energooszczędność jako nowy priorytet

Dawniej główną metryką był często surowy performance (FLOPS, MIPS, wynik w SPEC). Dziś równie ważne jest, ile energii trzeba zapłacić za jednostkę pracy. Krytyczne stały się metryki typu performance-per-watt, FPS-per-watt czy instrukcje na dżul.

Powodów jest kilka:

- Urządzenia mobilne – smartfony, laptopy, IoT żyją na baterii, więc każdy dodatkowy wat to mniejszy czas pracy i trudniejsze chłodzenie w ograniczonej obudowie.

- Centra danych – koszt energii i chłodzenia stanowi ogromną część OPEX. Zmniejszenie poboru mocy o kilkanaście procent przy tej samej wydajności przekłada się na realne miliony w rachunkach.

- Ograniczenia infrastruktury – gęstość upakowania serwerów w szafie i całkowita moc przyłączeniowa mają limity, których nie da się przekroczyć bez poważnych inwestycji.

To przesunięcie priorytetów widać w projektowaniu rdzeni: pojawiają się architektury heterogeniczne, łączące duże, szybkie rdzenie (P-core, „performance”) z małymi, energooszczędnymi rdzeniami (E-core, „efficiency”). Idea jest prosta: proste zadania i praca w tle lądują na energooszczędnych rdzeniach, a pełna moc odpalana jest tylko wtedy, gdy to rzeczywiście potrzebne.

Znaczenie specjalizowanych jednostek: GPU, NPU i akceleratory

Wraz z końcem darmowego przyrostu wydajności ogólnego CPU coraz większą rolę zaczęły odgrywać akceleratory domenowe – układy zaprojektowane pod konkretne klasy zadań. Najbardziej widoczne przykłady to:

- GPU – pierwotnie do grafiki 3D, dziś szeroko wykorzystywane w GPGPU (ogólne obliczenia równoległe), w tym w uczeniu maszynowym, renderingu, symulacjach numerycznych.

- NPU / TPU / akceleratory AI – wyspecjalizowane jednostki do operacji macierzowych i tensorowych (MAC – Multiply-Accumulate), zoptymalizowane pod inference i/lub trening sieci neuronowych.

- DSP – procesory sygnałowe do przetwarzania audio, obrazu, sygnałów radiowych.

- Akceleratory kryptograficzne – jednostki do szyfrowania, podpisów, obliczeń na krzywych eliptycznych.

Kluczowe jest to, że prawo Moore’a nadal działa – mamy wciąż coraz więcej tranzystorów – ale nie są one już w całości przeznaczane na ogólnego typu rdzenie CPU. Coraz większa ich część trafia do wyspecjalizowanych bloków, które dla wybranych zadań oferują kilkukrotnie lub wielokrotnie lepszy stosunek wydajności do poboru mocy niż klasyczny rdzeń ogólnego przeznaczenia.

Przykład z praktyki: smartfon, który w benchmarku CPU nie bije rekordów, może wciąż błyskawicznie obrabiać zdjęcia nocne czy wykonywać rozpoznawanie obrazu w czasie rzeczywistym właśnie dlatego, że intensywne zadania wędrują na ISP (Image Signal Processor) i NPU, a nie na tradycyjny CPU.

Nowe wąskie gardła: pamięć, I/O i komunikacja

Pamięć jako hamulec dla prawa Moore’a

Przez długie lata wykresy wydajności CPU rosły szybciej niż możliwości podsystemu pamięci. Efekt to klasyczna przepaść między tym, jak szybko rdzeń potrafi wykonywać instrukcje, a jak wolno docierają do niego dane z RAM. To zjawisko bywa nazywane „memory wall”.

Współczesny procesor jest w stanie w jednym cyklu wykonać kilka instrukcji, ale dostęp do pamięci DRAM liczony jest w dziesiątkach–setkach cykli. Cała nowoczesna hierarchia pamięci (L1, L2, L3, a czasem jeszcze L4/eDRAM) to próba złagodzenia tego zderzenia:

- Cache L1 – bardzo mała, ekstremalnie szybka (kilka cykli), podzielona na część dla danych i instrukcji.

- Cache L2 – większa, nieco wolniejsza (kilkanaście cykli), zwykle prywatna dla rdzenia.

- Cache L3 (LLC) – współdzielona między rdzeniami, duża, ale już wyraźnie wolniejsza (dziesiątki cykli).

Przyrost liczby tranzystorów pozwolił rozbudować cache kilkukrotnie, jednak opóźnienia DRAM nie skurczyły się w takim tempie jak rozmiary tranzystorów. Z punktu widzenia prawa Moore’a oznacza to, że teoretyczna moc obliczeniowa rośnie szybciej niż realnie dostępna przepustowość danych. W praktyce coraz częściej brakuje „paliwa” dla jednostek wykonawczych.

Efekt widać w prostym scenariuszu: odpalasz kompilację dużego projektu lub analizę danych. CPU skacze na 100%, ale gdy spojrzeć na profil wydajności, okazuje się, że znaczną część czasu rdzenie spędzają w stanie „stalled” – czekając na dane z pamięci.

Nowe pamięci i pakowanie 3D

Aby zmniejszyć dystans między logiką a pamięcią, branża sięgnęła po dwie ścieżki: nowe typy pamięci oraz nowe sposoby integracji.

Najbardziej widoczne przykłady to:

- HBM (High Bandwidth Memory) – pamięć DRAM układana w stos (3D) i łączona z GPU/CPU za pośrednictwem interposerów krzemowych. Zamiast kilku wąskich kanałów jak w DDR, HBM oferuje bardzo szeroką magistralę przy umiarkowanej częstotliwości, co daje ogromną przepustowość przy dobrym stosunku performance-per-watt.

- LPDDR / GDDR – wyspecjalizowane warianty DRAM optymalizowane pod mobilność (LP, Low Power) lub grafikę (GDDR – wysoka przepustowość), coraz ciaśniej zintegrowane z SoC i kontrolerami pamięci.

- Pamięci NVRAM / SCM – klasy takie jak 3D XPoint, MRAM czy ReRAM, próbujące wypełnić lukę między RAM a SSD. Opóźnienia większe niż DRAM, ale mniejsze niż klasyczne NAND, przy nieulotności danych.

Równolegle przyspieszyły prace nad integracją 2.5D i 3D:

- Interposery krzemowe – duże płytki krzemu z gęstą siecią połączeń, na których osadza się kilka „chipletów”: CPU/GPU, HBM, układy I/O. Dystans elektryczny między układami skraca się o rząd wielkości w porównaniu z klasycznym PCB.

- TSV (Through-Silicon Vias) – pionowe przelotki w krzemie, które umożliwiają łączenie warstw układów jedna nad drugą. To fundament pamięci HBM i pierwszych eksperymentów z logic stacking (układanie logiki i pamięci w jednym stosie).

Z perspektywy prawa Moore’a to ważne: dalszy wzrost liczby tranzystorów w samym die logicznym przynosi coraz mniejsze korzyści, jeśli nie ma jak ich nakarmić danymi. Do gry wchodzą więc „systemy w stosie” – kumulowanie nie tylko tranzystorów, ale i przepustowości w trzecim wymiarze.

Interkonekty i opóźnienia między układami

Nawet jeśli uda się „przyspieszyć” pamięć względem CPU, ciągle pozostaje szereg innych wąskich gardeł: komunikacja między chipami, między serwerami w szafie, a wreszcie między centrami danych. Wraz ze wzrostem mocy obliczeniowej rośnie gęstość ruchu na wszystkich poziomach.

Nowoczesne procesory i GPU korzystają z zaawansowanych interfejsów:

- PCI Express (PCIe) – standard ogólnego przeznaczenia, który z każdą generacją (3.0, 4.0, 5.0, 6.0) niemal podwaja przepustowość na linię, kosztem rosnącej złożoności sygnałowej i wymagań co do jakości ścieżek.

- CXL (Compute Express Link) – protokół nad PCIe, który umożliwia koherentny dostęp do pamięci pomiędzy CPU, GPU, NPU i innymi akceleratorami. To próba rozszerzenia „spójnego świata cache” poza pojedynczy socket CPU.

- NVLink / Infinity Fabric / własne interkonekty – szyte na miarę magistrale dla połączeń GPU–GPU, GPU–CPU lub CPU–chiplet, zanurzone głęboko w pakiecie.

Każdy krok w górę skali – od pojedynczego układu, przez płytę główną, szafę, aż po sieć między data center – dodaje własne opóźnienia, ograniczenia energetyczne i problemy z integralnością sygnału. Prawo Moore’a nie obejmuje tych warstw wprost, dlatego dziś ogromna część wysiłku inżynierskiego w HPC i chmurze dotyczy nie samego „liczenia”, ale przesuwania bitów w możliwie efektywny sposób.

Chipletowe SoC: rozbijanie monolitu

W pewnym momencie dalsze powiększanie pojedynczego monolitycznego układu przestało się opłacać. Yield spada, ryzyko defektów rośnie, a koszt mask i procesu litograficznego w nowym węźle (np. 5 nm, 3 nm) staje się ogromny. Stąd zwrot w stronę architektury chipletowej.

Zamiast jednego wielkiego die, projekt dzieli się na kilka mniejszych:

- Chiplet CPU – zawiera rdzenie, cache L2/L3 i lokalne interkonekty.

- Chiplet I/O – kontrolery pamięci, PCIe, USB, sieciówki, czasami również analog.

- Chiplet akceleratorów – GPU, NPU, DSP, dedykowane bloki.

Łączy je dedykowana magistrala w pakiecie (np. Infinity Fabric, EMIB, Foveros). Taki podział ma kilka zalet:

- Elastyczność procesu – logiczny rdzeń można wytwarzać w najnowszym, najdroższym węźle (np. 3 nm), a kontrolery I/O czy analog w starszym, tańszym (np. 12 nm), gdzie parametry sygnałowe są wręcz lepsze.

- Skalowanie produktów – ten sam chiplet CPU może trafić do układów 6-, 8-, 16-rdzeniowych, po prostu w innej konfiguracji i liczbie.

- Lepszy yield – małe kostki mają statystycznie mniej defektów, więc rośnie odsetek w pełni sprawnych die.

Z punktu widzenia prawa Moore’a tranzystory wciąż przybywają, ale ich fizyczna organizacja przestaje być jednorodna. Układ scalony coraz bardziej przypomina małą płytę główną zamkniętą w jednym opakowaniu, z własną wewnętrzną topologią i hierarchią komunikacji.

Koniec „czystego” skalowania a początek ery architektury systemowej

Tradycyjne odczytanie prawa Moore’a sugerowało: wystarczy zmniejszać tranzystory, a wszystko – wydajność, gęstość, koszt – samo „magicznie” się poprawi. Dziś to już nie działa w tej prostej formie. Oprócz samego procesu litograficznego kluczowe stały się decyzje architektoniczne na poziomie całego systemu.

Na praktycznym poziomie oznacza to, że inżynierowie pytają nie tylko: Jak szybki jest pojedynczy rdzeń?, ale raczej:

- Jak rozłożyć budżet mocy między rdzenie, cache, interkonekty i pamięć?

- Ile opłaca się zainwestować w uniwersalny CPU, a ile w akceleratory domenowe?

- Jakie topologie sieci wewnątrz układu (mesh, ring, crossbar) dają najlepszy kompromis między opóźnieniem a skalowalnością?

- Jakie klasy zadań są najczęstsze i pod nie optymalizować pipeline i jednostki wykonawcze?

Ponieważ proste zwiększanie częstotliwości i liczby tranzystorów przestało być tanie, rośnie rola optymalizacji „w poziomie” – projektowania całych platform, nie tylko pojedynczych rdzeni. To widać w serwerach (współpraca CPU+GPU+NPU), w konsolach (SoC integrujące CPU, GPU, kontrolery pamięci i audio) i w smartfonach (duże, heterogeniczne SoC z ISP, NPU, modemem, DSP audio).

Ekonomia procesu: czy miniaturyzacja dalej się opłaca?

Nawet jeśli fizycy i inżynierowie są w stanie upakować więcej tranzystorów na milimetrze kwadratowym, pozostaje pytanie, czy biznesowo ma to sens. Koszt pojedynczego węzła litograficznego eksploduje – zarówno pod względem sprzętu (maszyny EUV), jak i projektowania (setki inżynierów, złożone reguły DRC, warianty masek).

W uproszczeniu:

- Starsze węzły (np. 28 nm, 40 nm) – tańsze w produkcji, świetne do układów analogowych, mikrokontrolerów, prostych SoC, gdzie liczy się koszt i niezawodność, a nie maksymalna wydajność.

- Nowe węzły (np. 5 nm, 3 nm) – ekstremalnie drogie, stosowane tam, gdzie każdy procent wydajności i oszczędności energii przelicza się na realne zyski (flagowe smartfony, HPC, serwery chmurowe, topowe GPU).

Efekt uboczny: prawo Moore’a staje się coraz bardziej selektywne. Topowe, drogie układy nadal korzystają z miniaturyzacji tranzystorów w klasycznym sensie, ale ogromna masa elektroniki użytkowej bierze udział w zupełnie innym wyścigu – optymalizacji kosztu, niezawodności i czasu projektowania na ustalonym węźle.

Do tego dochodzi rosnący koszt projektowania samego układu: walidacja fizyczna, symulacje SI/PI (signal integrity / power integrity), weryfikacja formalna, bezpieczeństwo sprzętowe. Częstokroć software i hardware są współprojektowane, aby zamknąć wymagania wydajnościowe bez konieczności przeskoku na droższy proces.

Prawo Moore’a a software: dlaczego optymalizacja znowu ma znaczenie

Przy rosnącej złożoności sprzętu łatwo wpaść w pułapkę: „sprzęt i tak będzie szybszy”. Kilka dekad beztroskiego skalowania sprawiło, że oprogramowanie często rozrastało się bez większych zahamowań – pamięć taniała, CPU przyspieszało, więc słaba efektywność nie bolała tak bardzo.

Teraz sytuacja się zmienia. Wzrost wydajności jednowątkowej spowolnił, a architektury są coraz bardziej zróżnicowane (heterogeniczne SoC, akceleratory). W takich warunkach:

- profilowanie znów staje się obowiązkowe, nie „opcjonalne dla freaków performance’u”,

- świadome zarządzanie pamięcią (lokalność, unikanie niepotrzebnych alokacji, przemyślane struktury danych) ma realny wpływ na odczuwalną szybkość,

- zrównoleglanie kodu wymaga nie tylko wątków, ale także dobrania właściwego typu równoległości: CPU vs GPU vs NPU.

Dobrym przykładem jest trening modeli ML. Jeszcze kilka lat temu część zadań dało się „przepchnąć” na CPU. Dziś, bez GPU lub wyspecjalizowanego akceleratora, wiele scenariuszy staje się po prostu nieopłacalnych czasowo i energetycznie. Sam GPU to jednak za mało – kluczowe jest takie napisanie kodu (kerneli, pipeline’u danych), by efektywnie korzystał z dostępnej przepustowości i uniknął wąskich gardeł na poziomie I/O.

Nowe paradygmaty: od klasycznego CMOS do alternatyw

Pod spodem całego prawa Moore’a leży technologia CMOS, która przez dekady dostarczała tańsze, mniejsze i szybsze tranzystory. Coraz wyraźniej widać jednak, że ten silnik zaczyna tracić impet. Z tego powodu rosną inwestycje w alternatywne i uzupełniające paradygmaty obliczeń.

Kilka przykładowych kierunków:

- Obliczenia neuromorficzne – układy próbujące naśladować strukturę i działanie biologicznych sieci neuronowych (np. leaky integrate-and-fire), dążące do ekstremalnie niskiego zużycia energii w zadaniach rozpoznawania wzorców.

- Obliczenia in-memory / near-memory – przesuwanie części logiki bezpośrednio do pamięci (np. dodawanie, porównania czy proste operacje logiczne wykonywane „w” lub tuż „obok” macierzy DRAM/flash), aby ograniczyć ruch danych.

- Komputery kwantowe – działające na zupełnie innym modelu matematycznym (kubity, superpozycja, splątanie). Przydatne głównie w specyficznych zadaniach (optymalizacja, kryptografia, symulacje kwantowe), daleko im do zastąpienia uniwersalnego CPU, ale w dłuższym horyzoncie mogą zmienić rozkład sił w niektórych dziedzinach.

Najczęściej zadawane pytania (FAQ)

Czym właściwie jest prawo Moore’a w oryginalnym znaczeniu?

Oryginalne prawo Moore’a mówi o tym, że liczba elementów (głównie tranzystorów) możliwych do „upchnięcia” na pojedynczym układzie scalonym podwaja się co określony czas. Najpierw Moore szacował ten okres na około rok, później skorygował go do 18–24 miesięcy.

Chodzi więc o gęstość integracji (liczbę tranzystorów na danym obszarze krzemu), a nie bezpośrednio o „moc obliczeniową” czy częstotliwość taktowania. Więcej tranzystorów daje potencjał na większą wydajność, ale to, jak jest wykorzystany, zależy od architektury układu, pamięci, oprogramowania i wielu innych czynników.

Czy prawo Moore’a dotyczy wydajności procesorów czy liczby tranzystorów?

Prawo Moore’a w ścisłym sensie dotyczy wyłącznie liczby elementów (tranzystorów, diod, rezystorów) na układzie scalonym, czyli gęstości integracji. Dopiero wtórnie przekłada się to na potencjalny wzrost wydajności, jeśli projektanci odpowiednio wykorzystają dodatkowe tranzystory.

W mediach często myli się to z „podwajaniem wydajności komputerów”, co jest uproszczeniem. Przykład: dwa procesory w tym samym procesie technologicznym mogą mieć bardzo różną wydajność, jeśli jeden ma duże pamięci cache i rozbudowane jednostki obliczeniowe, a drugi jest prostym, energooszczędnym układem wbudowanym – choć oba mogą mieć podobną liczbę tranzystorów.

Dlaczego dzisiejsze „7 nm”, „5 nm” czy „3 nm” nie odpowiadają realnym rozmiarom tranzystorów?

Historycznie liczba w nazwie węzła technologicznego (np. 180 nm, 90 nm) była w przybliżeniu równa długości bramki tranzystora lub minimalnej szerokości ścieżki metalowej. Przy dużych węzłach (130 nm i więcej) to dość dobrze się zgadzało.

Wraz z miniaturyzacją struktura tranzystora stała się bardziej trójwymiarowa (FinFET, GAAFET), a różne wymiary skalują się inaczej. Dodatkowo producenci zaczęli używać nazw węzłów marketingowo. Dzisiejsze „7 nm” czy „5 nm” to głównie etykieta generacji procesu, a nie bezpośredni wymiar geometryczny. Przy porównaniach sensownie jest patrzeć na realną gęstość tranzystorów (tranzystory/mm²) zamiast na sam numer węzła.

Czy prawo Moore’a naprawdę zwalnia lub „umiera”?

Tempo dokładnego podwajania liczby tranzystorów co 18–24 miesiące wyraźnie spowolniło. Każdy kolejny węzeł wymaga ekstremalnie kosztownych fabryk, bardziej skomplikowanej litografii (np. EUV) i nowych typów tranzystorów. W efekcie „kroki” między generacjami są większe czasowo i mniej regularne.

To nie znaczy, że rozwój się zatrzymał, ale krzywa jest znacznie mniej przewidywalna niż w latach 70.–90. Dodatkowo „postęp” coraz częściej wynika z innych źródeł: lepszych architektur, specjalizowanych układów (GPU, NPU), optymalizacji oprogramowania czy pakietowania 3D (stackowanie chipów), a nie tylko z samej miniaturyzacji tranzystorów.

Co to jest tranzystor w procesorze i po co wprowadzono FinFET i GAAFET?

W układach cyfrowych tranzystor MOSFET działa jak przełącznik: napięcie na bramce decyduje, czy między drenem a źródłem płynie prąd („1”), czy nie („0”). Z wielu takich przełączników buduje się bramki logiczne, rejestry, cache i całe jednostki wykonawcze procesora.

Planarne tranzystory MOSFET (płaskie) sprawdzały się dobrze do okolic 28 nm. Poniżej tego rozmiaru zaczęły dominować zjawiska niepożądane, jak duże prądy upływu i problemy z kontrolą kanału przewodzącego. FinFET (tranzystor z „płetwą”) i później GAAFET (bramka otaczająca kanał ze wszystkich stron) poprawiają kontrolę elektrostatyczną nad kanałem, dzięki czemu można dalej zmniejszać rozmiary tranzystorów bez drastycznego pogorszenia wycieków prądu i stabilności.

Dlaczego prawo Moore’a jest nazywane samospełniającą się prognozą?

Branża półprzewodnikowa przyjęła prawo Moore’a jako nieformalną mapę drogową. Producenci litografii, chemikaliów, sprzętu do produkcji, projektanci chipów i inwestorzy planowali swoje działania z założeniem wykładniczego wzrostu gęstości tranzystorów.

Efekt był taki, że ogromne środki finansowe i badawcze były organizowane właśnie po to, by utrzymać ten trend. „Prawo” nie opisywało więc stałej fizycznej jak grawitacja, ale tworzyło presję biznesowo-techniczną, która pchała całą branżę w kierunku coraz mniejszych i gęściej upakowanych tranzystorów.

Jak prawo Moore’a przełożyło się na realne doświadczenie użytkowników komputerów?

Stały spadek kosztu pojedynczego tranzystora sprawił, że za tę samą kwotę można było kupić znacznie mocniejszy komputer co kilka lat. Typowe doświadczenie: pecet kupiony trzy lata wcześniej wydawał się wyraźnie wolniejszy od nowego modelu w podobnej cenie.

Dzięki temu producenci oprogramowania mogli zakładać, że sprzęt „dogoni” rosnące wymagania aplikacji. Przykładowo gry 3D, przeglądarki internetowe czy systemy operacyjne stawały się coraz cięższe, ale dla przeciętnego użytkownika bilans był korzystny: więcej funkcji i lepsza responsywność przy porównywalnym wydatku na nowy komputer.

Źródła

- Cramming more components onto integrated circuits. Electronics Magazine (1965) – Oryginalny artykuł Gordona Moore’a formułujący prawo Moore’a

- Moore’s Law at 40. Intel Corporation (2005) – Historia i interpretacja prawa Moore’a z perspektywy Intela

- The History of the Integrated Circuit. IEEE History Center – Tło rozwoju układów scalonych i tranzystorów w latach 50. i 60.

- Gordon E. Moore Oral History Interview. Computer History Museum (2006) – Wspomnienia Moore’a o Fairchild, Intelu i genezie prawa Moore’a

- The Semiconductor Industry Association (SIA) History. Semiconductor Industry Association – Rozwój branży półprzewodników i znaczenie roadmap technologicznych

- ITRS 2.0: 2015 International Technology Roadmap for Semiconductors. Semiconductor Industry Association / IEEE (2015) – Roadmap rozwoju technologii półprzewodnikowych i gęstości integracji

- International Roadmap for Devices and Systems (IRDS). IEEE – Następca ITRS, prognozy skalowania tranzystorów i węzłów technologicznych

- MOSFET: Encyclopedia of Electronic Components, Vol. 1. Maker Media (2012) – Opis działania tranzystora MOSFET jako przełącznika cyfrowego